# Apollo Lake SoC SPI and Signed Master Image Profile (SMIP)

**Programming Guide**

June 2016

Revision 1.0

**Intel Confidential**

Document Number: CDI/IBP# 559702

You may not use or facilitate the use of this document in connection with any infringement or other legal analysis concerning Intel products described herein. You agree to grant Intel a non-exclusive, royalty-free license to any patent claim thereafter drafted which includes subject matter disclosed herein.

No license (express or implied, by estoppel or otherwise) to any intellectual property rights is granted by this document.

Intel technologies' features and benefits depend on system configuration and may require enabled hardware, software or service activation. Performance varies depending on system configuration. **No computer system can be absolutely secure.** Check with your system manufacturer or retailer or learn more at intel.com.

Intel technologies may require enabled hardware, specific software, or services activation. Check with your system manufacturer or retailer.

The products described may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Intel disclaims all express and implied warranties, including without limitation, the implied warranties of merchantability, fitness for a particular purpose, and non-infringement, as well as any warranty arising from course of performance, course of dealing, or usage in trade.

All information provided here is subject to change without notice. Contact your Intel representative to obtain the latest Intel product specifications and roadmaps

Copies of documents which have an order number and are referenced in this document may be obtained by calling 1-800-548-4725 or visit www.intel.com/design/literature.htm.

Intel processor numbers are not a measure of performance. Processor numbers differentiate features within each processor family, not across different processor families. Go to: http://www.intel.com/products/processor\_number.

The original equipment manufacturer must provide TPM functionality, which requires a TPM-supported BIOS. TPM functionality must be initialized and may not be available in all countries.

Intel, Core and the Intel logo are trademarks of Intel Corporation in the U.S. and/or other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © 2015-2016, Intel Corporation. All Rights Reserved.

# **Contents**

| 1 | Intro | oduction | า          |                                                                       | 9                                     |

|---|-------|----------|------------|-----------------------------------------------------------------------|---------------------------------------|

|   | 1.1   | Overvi   | ew         |                                                                       | 9                                     |

|   | 1.2   | Termin   | ology      |                                                                       | 10                                    |

|   | 1.3   | Refere   | nce Docui  | ments                                                                 | 11                                    |

| 2 | SPI   | Flash A  | rchitectu  | ıre                                                                   | 13                                    |

| _ | 2.1   |          |            |                                                                       |                                       |

|   | 2.1   |          |            | coverable Parameter (SFDP)                                            |                                       |

|   | 2.2   |          |            | overable Parameter (SPDP)                                             |                                       |

|   |       | SPI Fa   | St Read    | Notform Module (Intal® TDM) on CDI Due                                | 13                                    |

|   | 2.4   |          |            | Platform Module (Intel® TPM) on SPI Bus                               |                                       |

|   | 2.5   |          |            | PL SoC                                                                |                                       |

|   | 2.6   |          |            |                                                                       |                                       |

|   |       | 2.6.1    |            | egion Layout                                                          |                                       |

|   |       | 2.6.2    |            | egion Sizes                                                           |                                       |

|   | 2.7   | Hardw    | are Seque  | encing                                                                | 15                                    |

| 3 | SPLI  | Flash Co | ompatibi   | lity Requirement                                                      | 17                                    |

|   | 3.1   | Anollo   | Lake SoC   | SPI Flash Requirements                                                | 17                                    |

|   | 5.1   | 3.1.1    |            | Requirements                                                          |                                       |

|   |       | 3.1.1    |            | D (Opcode 9Fh)                                                        |                                       |

|   |       | 3.1.2    |            | Page Write Usage Model                                                |                                       |

|   |       |          |            |                                                                       |                                       |

|   | 3.2   | 3.1.4    |            | re Sequencing Requirementsand DC Electrical Compatibility Guidelines  |                                       |

|   |       |          |            | ·                                                                     |                                       |

| 4 | Flash | n Descri | iptor      |                                                                       | 21                                    |

|   | 4.1   | Flash [  | Descriptor | Content                                                               | 22                                    |

|   |       | 4.1.1    | Descript   | or Signature and Map                                                  | 23                                    |

|   |       |          | 4.1.1.1    | FLVALSIG - Flash Valid Signature                                      |                                       |

|   |       |          |            | (Flash Descriptor Records)                                            | 23                                    |

|   |       |          | 4.1.1.2    | FLMAPO - Flash Map O Register                                         |                                       |

|   |       |          |            | (Flash Descriptor Records)                                            | 23                                    |

|   |       |          | 4.1.1.3    |                                                                       |                                       |

|   |       |          |            | (Flash Descriptor Records)                                            | 24                                    |

|   |       |          | 4.1.1.4    | FLMAP2—Flash Map 2 Register                                           |                                       |

|   |       |          |            | (Flash Descriptor Records)                                            |                                       |

|   |       | 4.1.2    |            | escriptor Component Section                                           | 25                                    |

|   |       |          | 4.1.2.1    | FLCOMP—Flash Components Register                                      |                                       |

|   |       |          | 4400       | (Flash Descriptor Records)                                            | 25                                    |

|   |       |          | 4.1.2.2    | FLILL—Flash Invalid Instructions Register                             | 27                                    |

|   |       |          | 4122       | (Flash Descriptor Records)                                            | 21                                    |

|   |       |          | 4.1.2.3    | FLILL1—Flash Invalid Instructions Register (Flash Descriptor Records) | 27                                    |

|   |       | 4.1.3    | Elach Do   | escriptor Region Section                                              |                                       |

|   |       | 4.1.3    |            | FLREGO—Flash Region 0 (Flash Descriptor) Register                     |                                       |

|   |       |          | 4.1.3.1    | (Flash Descriptor Records)                                            | 20                                    |

|   |       |          | 4.1.3.2    | FLREG1—Flash Region 1 (IFWI) Register                                 |                                       |

|   |       |          | 4.1.5.2    | (Flash Descriptor Records)                                            | 29                                    |

|   |       |          | 4.1.3.3    | (Flash Descriptor Records)                                            |                                       |

|   |       |          | 1.1.0.0    | (Flash Descriptor Records)                                            | 29                                    |

|   |       |          | 4.1.3.4    | FLREG4—Flash Region 4 (Platform Data Region) Register                 | · · · · · · · · · · · · · · · · · · · |

|   |       |          |            | (Flash Descriptor Records)                                            | 30                                    |

|   |       |          | 4.1.3.5    | FLREG5—Flash Region 5 (Device Expansion) Register                     |                                       |

|   |       |          |            | (Flash Descriptor Records)                                            | 30                                    |

|   |                   | 4.1.4                      | Flash Descriptor Master Section                                                                                                                                                         | 30                   |

|---|-------------------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

|   |                   |                            | 4.1.4.1 FLMSTR1—Flash Master 1 (Host CPU/ BIOS)                                                                                                                                         | 31                   |

|   |                   |                            | 4.1.4.2 FLMSTR2—Flash Master 2 (Intel® TXE)                                                                                                                                             |                      |

|   |                   | 4.1.5                      | SoC Softstraps                                                                                                                                                                          | 31                   |

|   |                   | 4.1.6                      | Descriptor Upper Map Section                                                                                                                                                            | 32                   |

|   |                   |                            | 4.1.6.1 FLUMAP1—Flash Upper Map 1 (Flash Descriptor Records)                                                                                                                            | 2.2                  |

|   |                   | 117                        |                                                                                                                                                                                         |                      |

|   |                   | 4.1.7                      | Intel® TXE Vendor Specific Component Capabilities Table                                                                                                                                 | 32                   |

|   |                   |                            | 4.1.7.1 JID0—JEDEC-ID 0 Register (Flash Descriptor Records)                                                                                                                             | 2.2                  |

|   |                   |                            | 4.1.7.2 VSCC0—Vendor Specific Component Capabilities 0                                                                                                                                  | 32                   |

|   |                   |                            | (Flash Descriptor Records)                                                                                                                                                              | 33                   |

|   |                   |                            | 4.1.7.3 JIDn—JEDEC-ID Register n                                                                                                                                                        |                      |

|   |                   |                            | (Flash Descriptor Records)                                                                                                                                                              | 33                   |

|   |                   |                            | 4.1.7.4 VSCCn—Vendor Specific Component Capabilities n                                                                                                                                  |                      |

|   |                   |                            | (Flash Descriptor Records)                                                                                                                                                              |                      |

|   | 4.2               |                            | ection                                                                                                                                                                                  |                      |

|   | 4.3               | _                          | Access Control                                                                                                                                                                          |                      |

|   |                   | 4.3.1                      | Intel Recommended Permissions for Region Access                                                                                                                                         |                      |

|   |                   | 4.3.2                      | Overriding Region Access                                                                                                                                                                | 34                   |

|   | 4.4               |                            | TXE Vendor-Specific Component Capabilities (Intel® TXE VSCC) Table                                                                                                                      | 35                   |

|   |                   | 4.4.1                      | How to Set a VSCC Entry in Intel® TXE VSCC Table for Apollo Lake Platfor                                                                                                                | rms . 35             |

|   |                   | 4.4.2                      | Intel® TXE VSCC Table Settings for Apollo Lake Systems                                                                                                                                  |                      |

| 5 | Seria             |                            | Discoverable Parameter (SFDP)                                                                                                                                                           |                      |

|   | 5.1               |                            | ew                                                                                                                                                                                      |                      |

|   | 5.2               |                            | erable Parameter Opcode and Flash Cycle                                                                                                                                                 |                      |

|   | 5.3               |                            | eter Table Supported on SoC                                                                                                                                                             |                      |

|   | 5.4               | Detaile                    | d JEDEC Specification                                                                                                                                                                   | 40                   |

| 6 | BIOS              | Config                     | uration for SPI Flash Access                                                                                                                                                            | 41                   |

|   | 6.1               | Unlock                     | ing SPI Flash Device Protection for Apollo Lake Platform                                                                                                                                | 41                   |

|   | 6.2               |                            | g SPI Flash via Status Register                                                                                                                                                         |                      |

|   | 6.3               |                            | tected Range Register Recommendations                                                                                                                                                   |                      |

|   | 6.4               |                            | mendations for Flash Configuration Lockdown and Vendor Component Lock                                                                                                                   | Bits                 |

|   |                   | 42                         |                                                                                                                                                                                         |                      |

|   |                   | 6.4.1                      | Flash Configuration Lockdown                                                                                                                                                            |                      |

|   | , -               | 6.4.2                      | Vendor Component Lock                                                                                                                                                                   |                      |

|   | 6.5               |                            | endor Specific Component Control Registers (VSCC)                                                                                                                                       |                      |

|   | 6.6               |                            | SCC Register Settings                                                                                                                                                                   |                      |

| 7 |                   |                            | Disable for Debug/Flash Burning Purposes                                                                                                                                                |                      |

|   | 7.1               | Intel®                     | TXE Disable                                                                                                                                                                             | 49                   |

|   |                   | 7.1.1                      | Erasing/Programming Intel <sup>®</sup> TXE FW                                                                                                                                           | 49                   |

| 8 | Reco              | mmend                      | ations for SPI Flash Programming in Manufacturing Environments                                                                                                                          | 51                   |

| 9 |                   |                            | ptor SoC Configuration                                                                                                                                                                  |                      |

| • | 9.1               |                            | escriptor Record 0 (Flash Descriptor Records)                                                                                                                                           |                      |

|   | 9.2               |                            | escriptor Record 1 (Flash Descriptor Records)                                                                                                                                           |                      |

|   | 9.3               |                            | escriptor Record 2 (Flash Descriptor Records)                                                                                                                                           |                      |

|   |                   |                            | SCHDIOL RECOLU Z TEIASH DESCHDIOL RECOLUST                                                                                                                                              | 54                   |

|   | 9.4               | SoC De                     |                                                                                                                                                                                         |                      |

|   | 9.4<br>9.5        |                            | escriptor Record 3 (Flash Descriptor Records)                                                                                                                                           | 56                   |

|   | 9.5               | SoC De                     | escriptor Record 3 (Flash Descriptor Records)escriptor Record 4 (Flash Descriptor Records)                                                                                              | 56<br>57             |

|   |                   | SoC De                     | escriptor Record 3 (Flash Descriptor Records)                                                                                                                                           | 56<br>57<br>58       |

|   | 9.5<br>9.6        | SoC De<br>SoC De           | escriptor Record 3 (Flash Descriptor Records)escriptor Record 4 (Flash Descriptor Records)escriptor Record 5 (Flash Descriptor Records)                                                 | 56<br>57<br>58       |

|   | 9.5<br>9.6<br>9.7 | SoC De<br>SoC De<br>SoC De | escriptor Record 3 (Flash Descriptor Records) escriptor Record 4 (Flash Descriptor Records) escriptor Record 5 (Flash Descriptor Records) escriptor Record 6 (Flash Descriptor Records) | 56<br>57<br>58<br>59 |

|     | 9.11<br>9.12<br>9.13<br>9.14<br>9.15<br>9.16 | SoC Descriptor Record 10 (Flash Descriptor Records)  SoC Descriptor Record 11 (Flash Descriptor Records)  SoC Descriptor Record 12a (Flash Descriptor Records)  SoC Descriptor Record 12b (Flash Descriptor Records)  SoC Descriptor Record 13 (Flash Descriptor Records)  SoC Descriptor Record 14 (Flash Descriptor Records) | . 62<br>. 62<br>. 62<br>. 63<br>. 63 |

|-----|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

|     | 9.17                                         | SoC Descriptor Record 15 (Flash Descriptor Records)                                                                                                                                                                                                                                                                            | . 63                                 |

| 10  | Signe                                        | ed Master Image Profile (SMIP)                                                                                                                                                                                                                                                                                                 | . 65                                 |

|     | 10.1                                         | Overview                                                                                                                                                                                                                                                                                                                       | . 65                                 |

|     | 10.2                                         | SMIP Tools                                                                                                                                                                                                                                                                                                                     | . 66                                 |

| 11  | Apoll                                        | o Lake TXE SMIP Configurations                                                                                                                                                                                                                                                                                                 | . 67                                 |

|     | 11.1                                         | OEM TXE SMIP (APL)                                                                                                                                                                                                                                                                                                             |                                      |

|     |                                              | 11.1.1 USB DnX (Descriptor) of TXE SMIP                                                                                                                                                                                                                                                                                        |                                      |

|     |                                              | 11.1.2 Soft Strap Section of TXE SMIP                                                                                                                                                                                                                                                                                          | . 68                                 |

|     |                                              | 11.1.2.1 Soft Strap Section for Apollo Lake Platform (APL A and B-Step)                                                                                                                                                                                                                                                        |                                      |

|     |                                              | 11.1.3 TPM Configuration and Boot Guard OEM Policy of TXE SMIP                                                                                                                                                                                                                                                                 | . 80                                 |

| 12  | SMIF                                         | Configurations                                                                                                                                                                                                                                                                                                                 | . 81                                 |

| -   | 12.1                                         | Apollo Lake Platform SMIP Configurations (APL A and B-Step)                                                                                                                                                                                                                                                                    |                                      |

|     | 12.1                                         | 12.1.1 Mod-Phy Lane Configuration Dependency with TXE SMIP                                                                                                                                                                                                                                                                     |                                      |

|     |                                              | 12.1.2 Mod-Phy Lane 2                                                                                                                                                                                                                                                                                                          |                                      |

|     |                                              | 12.1.3 Mod-Phy Lane 3                                                                                                                                                                                                                                                                                                          |                                      |

|     |                                              | 12.1.4 Mod-Phy Lane 4                                                                                                                                                                                                                                                                                                          |                                      |

|     |                                              | 12.1.5 Mod-Phy Lane 8                                                                                                                                                                                                                                                                                                          |                                      |

|     |                                              | 12.1.6 TCO_NO_REBOOT                                                                                                                                                                                                                                                                                                           | . 82                                 |

|     |                                              | 12.1.7 RESETBUTTON_DEBOUNCE_DIS                                                                                                                                                                                                                                                                                                |                                      |

|     |                                              | 12.1.8 LJ1PLL_SETTINGS_FORCE_COLD_RESET                                                                                                                                                                                                                                                                                        | . 82                                 |

|     |                                              | 12.1.9 SOIX_VR_RAMP_TIMER                                                                                                                                                                                                                                                                                                      |                                      |

|     |                                              | 12.1.10LJ1PLL_RW_CONTROL_1_DEFAULT                                                                                                                                                                                                                                                                                             |                                      |

|     |                                              | 12.1.11LJ1PLL_RW_CONTROL_2_DEFAULT                                                                                                                                                                                                                                                                                             |                                      |

|     |                                              | 12.1.12LJ1PLL_RW_CONTROL_3_DEFAULT                                                                                                                                                                                                                                                                                             |                                      |

|     |                                              | 12.1.13LJ1PLL_RW_CONTROL_5_DEFAULT                                                                                                                                                                                                                                                                                             |                                      |

|     |                                              | 12.1.14LCPLL_RW_CONTROL_1_DEFAULT                                                                                                                                                                                                                                                                                              |                                      |

|     |                                              | 12.1.15LCPLL_RW_CONTROL_2_DEFAULT                                                                                                                                                                                                                                                                                              |                                      |

|     |                                              | 12.1.16PMIC/VR Configuration                                                                                                                                                                                                                                                                                                   |                                      |

|     |                                              | 12.1.17 IASecureRdWrInValidAddrRange[0] to [12]                                                                                                                                                                                                                                                                                |                                      |

|     |                                              | 12.1.18IAInsecureRdWrInValidAddrRange[0] to [14]                                                                                                                                                                                                                                                                               |                                      |

|     |                                              | 12.1.20InsecureWrRegBitMskAddr[0] to [1]                                                                                                                                                                                                                                                                                       |                                      |

|     |                                              | 12.1.21 SecureWrRegBitMskAddr[0]                                                                                                                                                                                                                                                                                               |                                      |

|     |                                              | 12.1.2212C_VR_COMMON_CONFIG                                                                                                                                                                                                                                                                                                    |                                      |

|     | ures                                         |                                                                                                                                                                                                                                                                                                                                |                                      |

|     |                                              | Flash Regions Layout                                                                                                                                                                                                                                                                                                           |                                      |

|     |                                              | sh Descriptor (APL SoC)                                                                                                                                                                                                                                                                                                        |                                      |

|     |                                              | PR Read Instruction Sequence                                                                                                                                                                                                                                                                                                   |                                      |

|     |                                              | P Image Creation                                                                                                                                                                                                                                                                                                               |                                      |

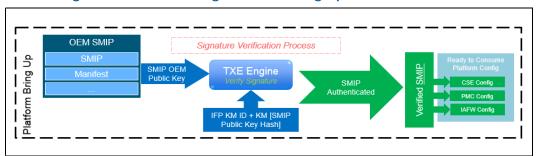

| '   | U-25IVII                                     | P image verification buring Platform Bring op                                                                                                                                                                                                                                                                                  | . 00                                 |

| Tal | oles                                         |                                                                                                                                                                                                                                                                                                                                |                                      |

| 4   | -1 Req                                       | ion Definition Template                                                                                                                                                                                                                                                                                                        | . 28                                 |

|     |                                              | ion Entries in Descriptor                                                                                                                                                                                                                                                                                                      |                                      |

| 4-3  | Flash Master Template                                                                    | .30  |

|------|------------------------------------------------------------------------------------------|------|

| 4-4  | Region Access Control Table Options                                                      | .34  |

|      | Recommended Read/Write Settings for Platforms                                            |      |

|      | Jidn - JEDEC ID Portion of Intel® TXE VSCC Table                                         |      |

| 4-7  | Vsccn – Vendor-Specific Component Capabilities Portion of the Apollo Lake SoC Platforms. | . 36 |

| 6-1  | VSCCO - Vendor-Specific Component Capabilities Register for SPI Component O              | .43  |

| 6-2  | VSCC1 - Vendor Specific Component Capabilities Register for SPI Component 1              | .45  |

| 6-3  | Description of How WSR and WEWS is Used                                                  | . 46 |

| 10-1 | 1SMIP Descriptor Table                                                                   | .65  |

# **Revision History**

| Document<br>Number Revision<br>Number              |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                   |

|----------------------------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| N/A 0.5                                            |     | Initial release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | June 2015         |

| 559702 0.55                                        |     | <ul> <li>Updated "Number of GPIO Profiles" to be 4 bytes instead of 2 in Section 11.1 and updated all offsets below this section</li> <li>Noted in Section 11.1.2 the outlined "Soft Straps" are for Apollo Lake platform (BXT not covered yet)</li> <li>Removed "Secure Touch" Configurations from GPIO Feature and Pin Configurations (set as reserved)</li> <li>Corrected Section 9.13 and Section 9.14 to be 64 bit in size</li> <li>Updated SMIP offset to be in hex indication in Section 11.1</li> <li>Added note in Section 11.1.1 that USB time will not be used at EOM</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | July 2015         |

| 559702                                             | 0.6 | <ul> <li>Added Section 11.1.2.2 for Broxton softstrap layout of TXE FW SMIP</li> <li>Updated FLCOMP table in Section 4.1.2.1:         <ul> <li>Added "Default Value" column to set values according to Intel RVP recommendations (default to hex: 125C02F5)</li> <li>Exposed "Read Clock Frequency" in bits 19:17</li> </ul> </li> <li>In Section 9.8, changed "IFP_PRE_BOOT_SOURCE" not to be visible in FIT</li> <li>In Section 11.1.2.1.13, Record 12a, PCIe x4 straps:</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | September<br>2015 |

| 559702                                             | 0.7 | <ul> <li>Added clarify for Figure 2-1</li> <li>Added recommendation for best performance on SPI frequency in Section 3.1</li> <li>Added clarification on SPI SFDP version requirement in Section 2.2</li> <li>Added Data Clear Security Policy in CSE SMIP in Section</li> <li>Added Platform SMIP Chapter 12, "SMIP Configurations"</li> <li>Added Mod-Phy Lane Dependency table between Platform Config SMIP &amp; TXE SMIP in Chapter 12, "SMIP Configurations"</li> <li>Set no usage bits to reserved: <ul> <li>Section 9.3, bit 10</li> <li>Section 9.8, bits 20:16, 12:11</li> <li>Section 11.1.2.2.3, bit 10</li> <li>Section 11.1.2.2.3, bit 23</li> </ul> </li> <li>Updated PUnit SMIP bits 9:6 with correct VR configuration default and configuration options in Section 11.1.2.1.1 &amp; Section 11.1.2.2.1</li> <li>Updated reserved bit default in Section 11.1.2.1.13, bit 14</li> <li>Update Secure NFC GPIO default configuration: <ul> <li>BXT RVP: Reset Pin Number</li> <li>BXT RVP: FW Update Pin Number</li> <li>Removed RPMC configurations as it is not POR.</li> </ul> </li> </ul> | October 2015      |

| • Set the follow straps to reserved (Section 9.8): |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | December 201      |

| Document Revision Number |     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Revision Date |

|--------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| 559702                   | 0.8 | <ul> <li>Added new"TPM Configuration and Boot Guard OEM Policy of TXE SMIP" to align with BXT B1 silicon, deltas from BXT A1:         <ul> <li>"TXE Straps (Record 7)": Updated/exposed bits 7:1 usages</li> <li>Added new "USBx Straps (Record 8b)" and adjusted record numbering</li> <li>Added new "FIA Straps (Record 9b)" and adjusted recording numbering</li> <li>Added updated Mex section to reflect new offsets now in "PCIe Straps (Record 10)"</li> <li>Updated "ISH Straps (Record 8a)" bits 15:8 default to 8'h50 instead of 8'h80</li> </ul> </li> <li>Added new ""</li> <li>Updated "Apollo Lake Platform SMIP Configurations (APL A and B-Step)":         <ul> <li>"LJ1PLL_RW_CONTROL_1_DEFAULT": Set bits 31:2 to reserved</li> <li>"LCPLL_RW_CONTROL_1_DEFAULT": Set bits 31:2 to reserved</li> <li>"IASecureRdWrInValidAddrRange[0] to [12]": Removed ranges IASecureRdWrInValidAddrRange[0] to [3]</li> <li>"IAIInsecureRdWrInValidAddrRange[0] to [14]": Removed ranges IAIInsecureRdWrInValidAddrRange[0]": Removed ranges IAI2CVRRdWrInValidAddrRange[0]": Removed ranges IAI2CVRRdWrInValidAddrRange[0]": Removed ranges InsecureWrRegBitMskAddr[0] to [1]": Removed ranges InsecureWrRegBitMskAddr[0] to [15]</li> <li>"SecureWrRegBitMskAddr[0]": Removed ranges SecureWrRegBitMskAddr[0]": Removed ranges SecureWrRegBitMskAddr[0] to [15]</li> </ul> </li> <li>Updates to "Soft Strap Section for Apollo Lake Platform (APL A and B-Step)"         <ul> <li>Section 11.1.2.1.10: Updated bits 3 &amp; 2 defaults to be Non-XHC</li> <li>Section 11.1.2.1.12: Updated this section as record12a to be the x2 Controller not the x4 Controller configuration. Updated bits 12:11 to reflect per x2 controller.</li> <li>Section 11.1.2.1.14: Updated this section as record 12b to be the x4 Controller not the x2 Controller configuration. Updated bits 12:11 to reflect per the x4 controller. A</li></ul></li></ul> | January 2016  |

| 559702                   | 1.0 | <ul> <li>General Update: Removed references of Broxton Platform</li> <li>Updated table in Section 4.1.2.1 FLCOMP:  — Bits [19:17] to be 3'h6 instead of 1'h0  — Bits [3:00] to be 4'h4 instead of 4'h5</li> <li>Updated Section 11.1.1 USB DnX Bits 67:36 and 35:4 description should be maximum 31 characters</li> <li>Set the following to reserved:  — "EXI Straps (Record 10)": Set bits 23:22 and 21:20 to reserved</li> <li>— "FIA Straps (Record 11)": Set bits 23:22, 21:22, 19:18 and 15:14 to reserved</li> <li>— "SATA Straps (Record 13)": Set bit 23:18 and15:4 to reserved as SATA Ports 7 to 2 are not applicable for APL</li> <li>Corrected Section 11.1.2.1.15 bits 1:0 description to show correct default per the default value</li> <li>Added note under "EXI Straps (Record 10)" and "FIA Straps (Record 11)"</li> <li>Added row a "TXE SMIP EXI (Record 10)" in table of "Mod-Phy Lane Configuration Dependency with TXE SMIP"</li> <li>Section 11.1 updates:  — Set offset 0xC8 to 0x167C to reserved and removed all sections in reference to these offsets as GPIO configurations have moved to TXE NVARs and no longer in TXE SMIP.</li> <li>— Set 0x16C4 to reserved.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | June 2016     |

### 1 Introduction

#### 1.1 Overview

This document is intended for OEMs and software vendors to clarify various aspects of programming the SPI flash and eMMC as well as SMIP on mIA based platforms. The current scope of this document is for Intel® microarchitecture code name Apollo Lake only for SPI and eMMC based platforms.

SMIP (Signed Master Image Profile) is a 16KB OEM signed critical sub-partition in the IFWI Image used for platform-specific data that firmware and software may find necessary in generating specific platform behavior.

SMIP is functionally similar to SPI soft straps. SPI Soft straps were only write-protected. SMIP is signature protected providing a common mechanism for all FW storage media.

Note:

SPI storage media is still required to carry descriptor settings relevant to SPI access. Currently, SMIP architecture supports configuration settings for TXE, PMC, and IAFW.

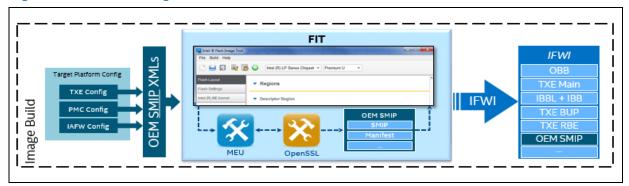

SMIP starts with SMIP Descriptor Table (SDT), which describes the size and offset of each of these blocks. The SMIP referred to as OEM SMIP, as it is configurable by OEMs using FIT Tool.

FIT tool will support SMIP input for various components through its GUI. OEMs can customize the SMIP settings and generate updated IFWI as required. Refer Chapter 10, "Signed Master Image Profile (SMIP)" and Chapter 12, "SMIP Configurations" for more details on SMIP layout and FIT support.

There will be differences in configuration recommendations for SMIP per platform. While SMIP layout will be the same for APL, configuration differences will apply. SPI related configurations only apply to APL, but all SMIP configurations apply to both platforms for SPI and eMMC. Separate sections and special notes will be in this document for platform specific recommendations.

The **OEM SMIP** sub-partition (**SMIP** = **Signed Master Image Profile**) contains OEM-signed configuration parameters for the platform. The sub-partition contains the following:

- A directory

- · A partition manifest

- · An SMIP structure, with a signed manifest

Here's an outline of the chapters to follow:

Chapter 2, "SPI Flash Architecture"

• Overview of SPI flash, Descriptor, Flash Layout, compatible SPI flash.

Chapter 3, "SPI Flash Compatibility Requirement"

• Overview of compatibility requirements for Apollo Lake products.

#### Chapter 4, "Flash Descriptor"

· Overview of the descriptor and Descriptor record definition

#### Chapter 5, "Serial Flash Discoverable Parameter (SFDP)"

· Overview of the SFDP definition.

#### Chapter 6, "BIOS Configuration for SPI Flash Access"

• Describes how to configure BIOS for SPI flash access.

#### Chapter 7, "Intel® TXE Disable for Debug/Flash Burning Purposes"

• Methods of disabling Intel Management Engine for debug purposes.

## Chapter 8, "Recommendations for SPI Flash Programming in Manufacturing Environments"

• Recommendations for manufacturing environments.

#### Chapter 9, "Flash Descriptor SoC Configuration"

• Flash Descriptor SoC Soft Strap Section.

#### Chapter 10, "Signed Master Image Profile (SMIP)"

· Overview of SMIP.

#### Chapter 11, "Apollo Lake TXE SMIP Configurations"

• Description and outline of TXE SMIP configurations

#### Chapter 12, "SMIP Configurations"

Description and outline of SMIP configurations

### 1.2 Terminology

| Term                   | Description                                                            |

|------------------------|------------------------------------------------------------------------|

| APL                    | Apollo Lake Platform                                                   |

| BIOS                   | Basic Input-Output System                                              |

| BPDT                   | Boot Partition Descriptor Table                                        |

| CRB                    | Customer Reference Board                                               |

| Intel <sup>®</sup> FPT | Intel <sup>®</sup> Flash Programming Tool - programs the SPI flash     |

| FPT                    | Flash Partition Table                                                  |

| Intel <sup>®</sup> FIT | Intel® Flash Image Tool – creates a flash image from separate binaries |

| FW                     | Firmware                                                               |

| Intel <sup>®</sup> TXE | Intel® Trusted Execution Engine (Intel® TXE FW)                        |

| IFWI                   | Integrated Firmware Image                                              |

| NVM                    | Non-Volatile Memory                                                    |

| LPC                    | Low Pin Count Bus- bus on where legacy devices such a FWH reside       |

| LVSCC                  | Lower Vendor Specific Component Capabilities                           |

| S-BPDT                 | Secondary Boot Partition Descriptor Table                              |

| SMIP                   | Signed Master Image Profile                                            |

| Term  | Description                                                                  |

|-------|------------------------------------------------------------------------------|

| SFDP  | Serial Flash Discoverable Parameter                                          |

| SoC   | System-on-a-Chip                                                             |

| SPI   | Serial Peripheral Interface – refers to serial flash memory in this document |

| UVSCC | Upper Vendor Specific Component Capabilities                                 |

| VSCC  | Vendor Specific Component Capabilities                                       |

### 1.3 Reference Documents

| Document                                        | Document # / Location                                                                                                                                     |

|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Apollo Lake External Design Specification (EDS) | Contact your Intel field representative.                                                                                                                  |

| Intel Flash Image Tool (FIT)                    | \System Tools\Flash Image Tool of latest Intel <sup>®</sup> TXE kit from VIP. The Kit MUST match the platform you intend to use the flash tools for.      |

| Intel Flash Programming Tool (FPT)              | \System Tools\Flash Programming Tool of latest Intel® TXE from VIP. The Kit MUST match the platform you intend to use the flash tools for.                |

| FW Bring Up Guide                               | Root directory of latest Intel <sup>®</sup> Trusted Execution Engine kit from VIP. The Kit MUST match the platform you intend to use the flash tools for. |

### 2 SPI Flash Architecture

### 2.1 Descriptor Mode

Apollo Lake platform supports up to two SPI flash devices. The SPI flash connected to Chip Select 0 must contain a valid Descriptor as defined in Chapter 4, "Flash Descriptor". The contents of the Descriptor provide platform configuration and enable the SoC to securely manage storage among multiple users/purposes.

SPI flash must be connected directly to the APL SoC SPI bus.

Note: APL SoC SPI controller only supports Descriptor mode (does not support non-descriptor mode).

Refer *SPI Supported Feature Overview* of the latest APL External Design Specification (EDS) of Apollo Lake platform for more detailed information.

### 2.2 Serial Flash Discoverable Parameter (SFDP)

Serial flash with SFDP have their supported capabilities and commands stored inside the serial flash devices. The controller will discover the attributes needed to operate.

APL SoC requires SPI flash devices support JEDEC standard JESD216 SDFDP v1.0 (Serial Flash Discoverable Parameters). Revision A (JESD216A) or later is strongly recommended but not mandatory. SFDP provides a consistent method of describing the functional and feature capabilities of SPI devices in a standard set of internal parameter tables. These parameter tables can be interrogated by the SoC to enable adjustment needed to accommodate divergent feature from multiple vendors.

Refer Chapter 5, "Serial Flash Discoverable Parameter (SFDP)" for more information.

#### 2.3 SPI Fast Read

**Note:** Refer **SPI for Flash** section of the latest APL External Design Specification (EDS) of Apollo Lake platform for more detailed information. 50-MHz support requires SPI component that meet 66-MHz timing.

# 2.4 Intel<sup>®</sup> Trusted Platform Module (Intel<sup>®</sup> TPM) on SPI Bus

APL SoC supports Intel TPM on the SPI bus.

Refer *Serial Peripheral Interface (SPI)* section of the latest APL SoC External Design Specification (EDS) of Apollo Lake platform for more detailed information.

### 2.5 Boot Flow for APL SoC

Refer Boot BIOS strap in the **Functional Straps** of the latest External Design Specification (EDS) of Apollo Lake platform for more detailed information.

### 2.6 Flash Regions

The controller can divide the SPI flash into separate regions below.

| Region | Content                                                                              |

|--------|--------------------------------------------------------------------------------------|

| 0      | Descriptor                                                                           |

| 1      | IFWI (Integrated Firmware Image)                                                     |

| 2      | TXE ROM Bypass - Intel® Trusted Execution Engine Firmware (Intel® TXE FW) ROM Bypass |

| 4      | PDR (Platform Data Region)                                                           |

| 5      | Device Expansion                                                                     |

**Note:** This is ROM Bypass region as shown in Figure 2-1, and not TXE FW region. This region is only used in pre-production environment.

### 2.6.1 Flash Region Layout

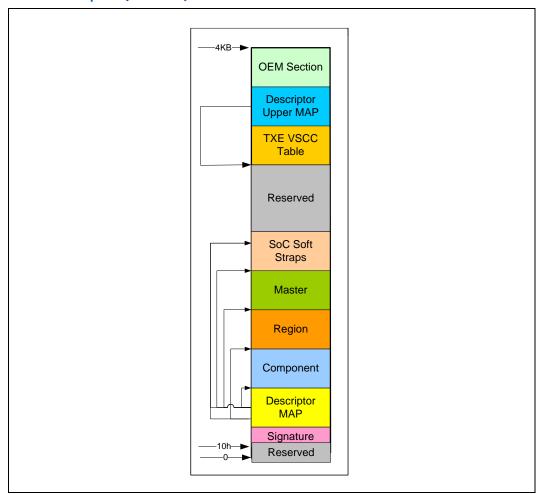

In the SPI controller, a 4K descriptor at the base of the SPI device splits the device into regions and defines the access control to each region.

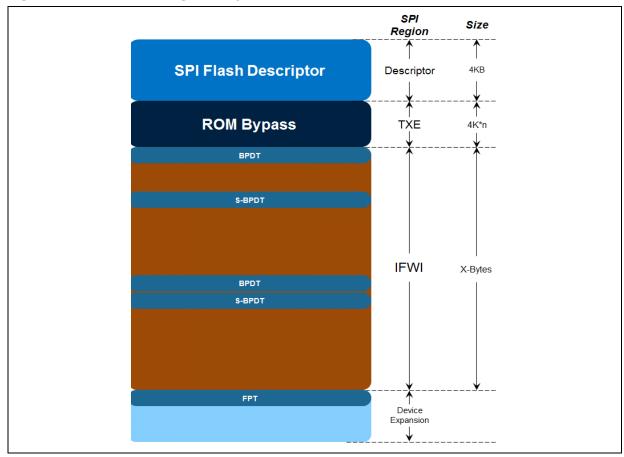

Figure 2-1. SPI Flash Regions Layout

As seen in Figure 2-1, the descriptor defines at least the following device regions:

- 1. **TXE ROM Bypass Region**: Starting from offset 4K. This region is used for TXE ROM Bypass. When TXE ROM Bypass does not exist, this region size is 0.

- 2. **IFWI Region**: This region starts after TXE ROM Bypass region spanning over the rest of the SPI flash until the next region (i.e. Device Expansion or other regions defined by OEM). Size is estimated to be at 7MB.

- 3. **Device Expansion**: The Size is defined at build time estimated to be 1MB.

**Note:** FPT in the above diagram is Flash Partition Table for TXE FW usage.

#### 2.6.2 Flash Region Sizes

SPI flash space requirements differ by platform and configuration. Refer to documentation specific to your platform for BIOS and TXE ROM Bypass Region flash size estimates.

Refer *SPI Flash Regions* section of the latest APL SoC External Design Specification (EDS) of Apollo Lake platform for more detailed information.

### 2.7 Hardware Sequencing

Host/Bios and TXE may read/write /erase flash via Hardware Sequencing or Software Sequencing registers.

APL SoC Hardware sequencing has been enhanced to include all operations the BIOS needs to perform.

**Note:** Host / Bios Software Sequencing is not supported in Apollo Lake.

**Note:** OEM EC may also have access to IFWI region.

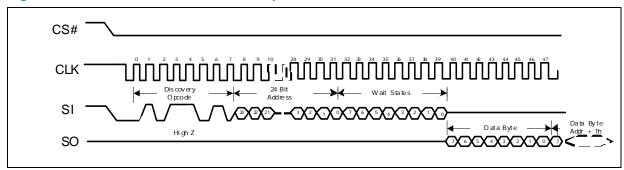

Hardware sequencing has a predefined list of opcodes, the SoC discovers the 4k and 64k erase opcodes via SFDP.

Refer **Serial Peripheral Interface Memory Mapped Configuration Registers** in *Apollo Lake External Design Specification (EDS)* for more details.

88

# 3 SPI Flash Compatibility Requirement

### 3.1 Apollo Lake SoC SPI Flash Requirements

- Apollo Lake SoC allows for up to two SPI flash devices to store BIOS, and Intel<sup>®</sup> TXE FW.

- Intel<sup>®</sup> TXE FW is required for Apollo Lake based platforms.

- Each SPI component can support up to 64 MB (128 MB total addressable) using 26-bit addressing

- 1.8V SPI I/O buffer VCC

- SPI Fast Read instruction is supported and frequency of 14MHz, 25MHz, 40MHz and 50MHz

- SPI Dual Output and Dual I/O Fast read instruction is supported with frequency of 14MHz, 25MHz, 40MHz and 50MHz

- SPI Quad Output and Quad I/O Fast read instruction is supported with frequency of 14MHz, 25MHz, 40MHz and 50MHz

Note:

In order to meet best performance, frequencies above must use the highest SPI configurations.

If there are two SPI components, both components have to support fast read in order to enable Fast Read.

Flash devices that contain a QE bit must be configured with QE=1. No special configuration is required for flash devices that support Quad mode but do not contain a Quad Enable (QE) bit. Several manufacturers offer SKU's with QE=1 by default.

#### 3.1.1 General Requirements

- Erase size capability of: 4 KBytes erase must be supported uniformly across the flash array. If 64k erase is also supported, then it must be supported uniformly across the flash array.

- Serial flash device must ignore the upper address bits such that an address of FFFFFFh aliases to the top of the flash memory.

- SPI Compatible Mode 0 support: Clock phase is 0 and data is latched on the rising edge of the clock.

- If the device receives a command that is not supported or incomplete (less than 8 bits), the device must discard the cycle gracefully without any impact on the flash content.

- An erase command (page, sector, block, chip and so on.) must set all bits inside the designated area (page, sector, block, chip and so on.) to 1 (Fh).

- Status Register bit 0 must be set to 1 when a write, erase or write to status register is in progress and cleared to 0 when a write or erase is NOT in progress.

- Devices requiring the Write Enable command must automatically clear the Write Enable Latch at the end of Data Program instructions.

- The flexibility to perform a write between 1 byte to 64 bytes is required.

- SFDP fields: dword 1, bit 4 "Write Enable Instruction". Dword 1, bit 3 "Volatile Status Register", both bits must be 0.

Intel Trusted Execution Engine Firmware must meet the SPI flash based BIOS Requirements plus:

- 2.2 Serial Flash Discoverable Parameter (SFDP)

- 3.1.2 JEDEC ID (Opcode 9Fh)

- 3.1.3 Multiple Page Write Usage Model

- 3.1.4 Hardware Sequencing Requirements

Write protection scheme must meet guidelines as defined in Section 3.1 Apollo Lake SoC SPI Flash Requirements.

#### 3.1.2 JEDEC ID (Opcode 9Fh)

Since each serial flash device may have unique capabilities and commands, the JEDEC ID is the necessary mechanism for identifying the device so the uniqueness of the device can be comprehended by the controller (master). The JEDEC ID uses the opcode 9Fh and a specified implementation and usage model. This JEDEC Standard Manufacturer and Device ID read method is defined in Standard JESD21-C, PRN03-NV1 and is available on the JEDEC website: www.jedec.org.

### 3.1.3 Multiple Page Write Usage Model

Intel platforms have firmware usage models require that the serial flash device support multiple writes to a page (minimum of 512 writes) without requiring a preceding erase command. BIOS commonly uses capabilities such as counters that are used for error logging and system boot progress logging. These counters are typically implemented by using byte-writes to 'increment' the bits within a page that have been designated as the counter. The Intel firmware usage models require the capability for multiple data updates within any given page. These data updates occur via byte-writes without executing a preceding erase to the given page. Both the BIOS and Intel Management Engine firmware multiple page write usage models apply to sequential and non-sequential data writes.

Flash parts must also support the writing of a single byte 1024 times in a single 256byte page without erase. There will be 64 pages where this usage model will occur. These 64 pages will be every 16 kilobytes.

### 3.1.4 Hardware Sequencing Requirements

The following table contains a list of commands and the asSoCiated opcodes that a SPI-based serial flash device must support in order to be compatible with hardware sequencing.

| Commands                           | OPCODE                        | Notes                                                                                                                   |

|------------------------------------|-------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| Write to Status<br>Register        | 01h                           | Writes a byte to SPI flash's status register. Enable Write to Status Register command must be run prior to this command |

| Program Data                       | 02h                           | Single byte or 64 byte write as determined by flash part capabilities and software                                      |

| Read Data                          | 03h                           |                                                                                                                         |

| Write Disable                      | 04h                           |                                                                                                                         |

| Read Status                        | 05h                           | Outputs contents of SPI flash's status register                                                                         |

| Write Enable                       | 06h                           |                                                                                                                         |

| Fast Read                          | 0Bh                           |                                                                                                                         |

| Enable Write to Status<br>Register | 06h                           | If write-status 01h requires a write-enable, then 06h must enable write-status.                                         |

| Erase                              | Programmable/<br>Discoverable | 4 Kbyte erase. Uses the value from SFDP (if available) else value from VSCCn Erase Opcode register value                |